# intel

# ISA Bus Specification and Application Notes

September 12, 1989

**OCPD** Technical Marketing

<u>Intel ISA Bus Specification</u> <u>and</u> <u>Application Notes</u>

Rev. 2.01

SEPTEMBER 12, 1989

With respect to information contained within this document, INTEL makes no warranties of merchantability or fitness for a particular purpose or any other warranties, representations or conditions, express or implied by statue, trade usage, or otherwise.

Furthermore, INTEL shall not be liable for any loss, claim, injury, special or consequential damages arising from the use of any information contained herein.

The information in this document is subject to change without notice.

Copyright 1989, Intel Corporation

.

## TABLE OF CONTENTS

| 1.0   | SCOPE                           | •                 | •••    | •••   | •            | •         | • •        | •        | •            | ٠    | •       | •        | •          | •    | •  | • | • | • | • | • | •   |   | • | 6          |

|-------|---------------------------------|-------------------|--------|-------|--------------|-----------|------------|----------|--------------|------|---------|----------|------------|------|----|---|---|---|---|---|-----|---|---|------------|

| 2.0   | NATUR                           | E OF              | THI    | s s   | PEC          | IF        | ICA        | TI       | ОМ           | •    | •       | •        | •          | •    | •  | • | • | • | • | • |     | • | • | 6          |

| 3.0   | CONVE                           | NTIO              | NS     | •••   | •            | •         |            | •        | •            | •    | •       | •        | •          | •    | •  | • | • | • |   | • | •   |   |   | 7          |

| 4.0   | ARCHI                           |                   |        |       |              |           |            |          |              |      |         |          |            |      |    |   |   |   |   |   |     |   |   | 8          |

| 5.0   |                                 |                   |        |       |              |           |            |          |              |      |         |          |            |      |    |   |   |   |   |   |     |   |   |            |

| 5.3   | BUS O                           | MADV.             | CDU    | RID   | JIE          | 5 4       | лип        | ום       | 221          | GN   | 1       | •        | •          | •    | •  | • | ٠ | • | • | • | •   | • | • | 10         |

|       |                                 | MARY              | TDOT   |       | •            | • •       | • •        | •        | •            | ٠    | •       | •        | •          | •    | •  | • | • | • | • | • | •   | • | • | 10         |

| 5.2   | 2 DMA                           | CUN               | TROL   | JUER  | •            | • •       | •          | •        | •            | •    | •       | •        | •          | •    | ٠  | ٠ | • | • | ٠ | • | •   | • | • | 13         |

|       | ADD                             | -ON (             | CARD   | 5.    | •            | •         | •          | •        | •            | •    | •       | •        | •          | •    | •  | • | • | • | • | • | •   | • |   | 15         |

| 5.4   | t REFI                          | RESH              | CON    | TRO   | LLE:         | R.        | •          | •        | •            | •    | •       | •        | •          | •    | •  | • | • | • | • | • | •   | • | • | 20         |

| 6.0   | NON-BI                          | JS OI             | WNER   | AT    | <b>FRI</b>   | BUJ       | res        | •        | •            | •    |         |          | •          | •    |    |   |   |   |   |   |     |   | _ | 24         |

| 0.1   | L MEMO                          | JRY 🖌             | ADDR   | ESS.  | -SP.         | ACI       | Ξ.         |          |              | -    | -       | -        |            |      |    |   |   |   |   |   |     |   |   | ~ 4        |

| 0.4   | 2 170                           | ADDI              | RESS   | SP    | ACE          |           |            |          |              |      |         |          |            |      |    |   |   |   |   |   |     |   |   |            |

| 0.3   | 2 INTI                          | LRRUI             | PT S   | TRUC  | "PU          | RE.       |            |          | -            |      |         |          |            |      |    |   |   |   |   |   |     |   |   |            |

| 6.4   | DAT                             | A SWA             | APPI   | NG    |              |           |            |          | -            |      |         |          |            | •    | •  | • | • | • | • | • | •   | • | • | 26         |

|       |                                 |                   |        |       |              |           |            |          |              |      |         |          |            |      |    |   |   |   |   |   |     |   |   |            |

| 7.0   | SIGNAL                          | L DES             | SCRI   | PTIC  | ONS          | •         | •          | ٠        | •            | •    | •       | •        | •          | •    | •  |   |   |   |   |   |     |   |   | 29         |

| / • 1 | L SIGI                          | NAL U             | GROU   | PS    | -            |           | -          |          | -            | -    |         |          |            |      |    |   |   |   |   |   |     |   |   | ~ ~        |

|       | / • <del>_</del> • <del>_</del> | AUUI              | KESS   | -SIC  | -NA          |           | RO         | UP.      |              |      |         |          |            |      |    |   |   |   |   |   |     |   |   |            |

|       | •                               |                   | பட்ட   | UNTI  | KOL.         | - 5 1     | GN         | ΑΙ.      | - ( - R      | O(1) | μ       |          |            |      |    |   |   |   |   |   |     |   |   | ~ ~        |

|       | · 1 • 3                         | CEN'              | FRAL   | - CON | 1TR          | ЭΤ.       | ST         | CN2      | <b>Ι</b> Τ.  | CP   | 011     | D        |            |      |    |   |   |   |   |   |     |   |   |            |

| 7     | 7.1.4                           | INTI              | ERRU   | PT S  | SIG          | IAI       | G          | ROT      | IP           |      |         | -        | •          | •    | •  | • | • | • | • | • | •   | • | • | 36         |

| 7     | 7.1.5                           | DIRI              | ЕСТ    | MEMO  | NBA          | 20        | CE.        | 22       | ст<br>С      | CN.  | א ד     | ່ດ       | DO         | מוזה | •  | • | • | • | • | • | •   | • | • | 37         |

| 7     | 7.1.6                           | POW               | ER G   | ROUI  | 2            |           |            | 55       | 01           | GI   | nL      | , G      | RU         | UF   |    | • | • | • | • | • | •   | • | • | 38         |

|       |                                 |                   |        |       |              |           |            |          |              |      |         |          |            |      |    |   |   |   |   |   |     |   |   |            |

| 8.0   | BUS CY                          | CLES              | 5.     | • •   | • •          |           | •          | •        | •            | •    | •       | •        | •          | •    | •  |   |   | • |   |   |     |   |   | 39         |

| . Ö.J | L ACCI                          | 255 (             | CACT   | ES .  |              | -IN       | TR         | וחכ      | ICT          | סדי  | N –     | -        |            |      |    |   |   |   |   |   |     |   |   |            |

| 2     | 5 • I • I                       | ACCI              | ESS    | CYCI  | JE .         |           | 0          | - WA     | TT           | S    | ጥእ      | ጥፑ       | _ T        | VD   | T. |   |   |   |   |   |     |   |   |            |

| 8     | 5.1.Z                           | ACCI              | ESS -  | CYCI  | ΤE .         |           | - N(       | าคง      | ΙΔΤ.         | . T  | VΡ      | F        |            |      |    |   |   |   |   |   |     |   |   |            |

| c     |                                 | ACCI              | 222    | CYCI  | ын: .        |           | - R1       | HΔT      | ۱V           | ΨV   | DF      |          |            |      |    |   |   |   |   |   |     |   |   |            |

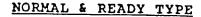

| 0.4   | : REFF                          | KESH              | CYC    | LES   |              | . 1       | NTT        | SUL      | nic          | TT.  | ∩N      |          |            |      |    |   |   |   |   |   |     |   |   |            |

| c     |                                 | - K P. P F        | KESH.  | - CYC | 11.ECS       | ÷ .       |            | NC       | мча          | ΔT.  | - TP    | νD       | r -        |      |    |   |   |   |   |   |     |   |   |            |

| · 8   | .2.2                            | REFE              | RESH   | cvc   | TEC          |           | ••         | DE       | יז גי<br>מגי | v i  | ±<br>mv | TL<br>DE | Ľ          | •    | •  | • | • | • | • | • | •   | • | • | 48         |

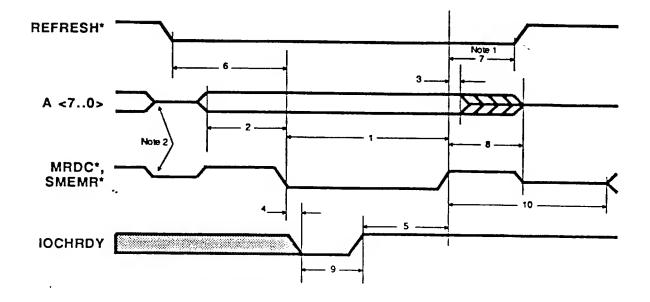

| 8.7   | ג את                            | TDAN              | ICEL.  |       |              |           | • •        | T        | NU<br>NU     |      |         | PE<br>OT | <b>T</b> ~ | •    | •  | • | • | • | ٠ | • | •   | • | • | 49         |

| 0.5   | DMA                             | DWY               | MDX    | K CI  |              | 20        | •••        | • 4      | NT.          | RO   | DU      | CT       | 10         | N    | •  | • | • | • | • | • | • ' | • | • | 51         |

| 0     | 3.3.1                           | DMA               | TRA    | NSFE  |              |           |            | • C      | ••           | N    | OR.     | MA<br>-  | L          | TY:  | PE |   | • | • | • | • | •   | • | • | 51         |

|       | 3.3.2                           | DMA               | TRA    | NSFE  | IR C         | SAC       | LES        | <b>.</b> | ••           | R    | EA      | DY       | T          | Y P  | E  | • | • | • | • | • | •   | • | - | 52         |

| 8.4   | BUS                             | OWNE              | SRSH   | IPC   | YCI          | LES       | •          | •        | •            | •    | •       | •        | •          | •    | •  | • | • | • | • | • | •   | • | • | 54         |

| 9.0   | BUS CY                          | CLE               | TIM    | ING   | SPE          | cs        | •          | •        | •            | •    | •       | •        | •          | •    | •  | • | • | • | • | • | •   | • | • | 5 <b>6</b> |

| 10.0  | SLOT                            | ልጥጥፔ              | יוופדג | TEC   |              |           |            |          |              |      |         |          |            |      |    |   |   |   |   |   |     |   |   |            |

| 10    | 1 SLC                           | יד דיי<br>דכד ידע | יערות  | 661V  | • •<br>• • • | •<br>תואי | <b>.</b> . | •        | •            | •    | •       | •        | •          | •    | •  | • | • | • | • | • | •   | • | • | 62         |

| ±V•   | - 510                           | ×1 L1             | in Mi  |       | INTIE        | 114 T.    | 5          | •        | •            | •    | •       | •        | •          | •    | •  | • | • | • | • | • | •   | • | • | 62         |

. •

| INTEL ISA Bus Specification and Application Notes Page     | : 3 |

|------------------------------------------------------------|-----|

| 10.3 BUS SIGNAL VOLTAGE & CURRENT LEVELS                   |     |

| 10.4 ADDITIONAL ADD-ON CARD DRIVER & RECEIVER REQUIREMENTS |     |

| 10.5 BACKPLANE RESISTORS                                   | 67  |

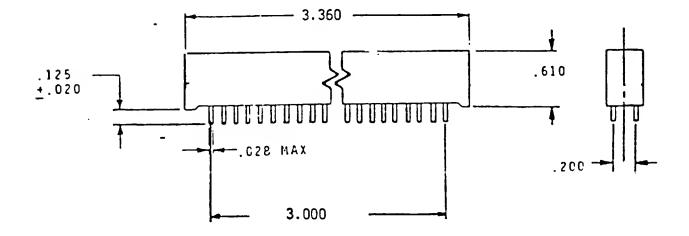

| 11.0 MECHANICAL SPECIFICATION                              | 68  |

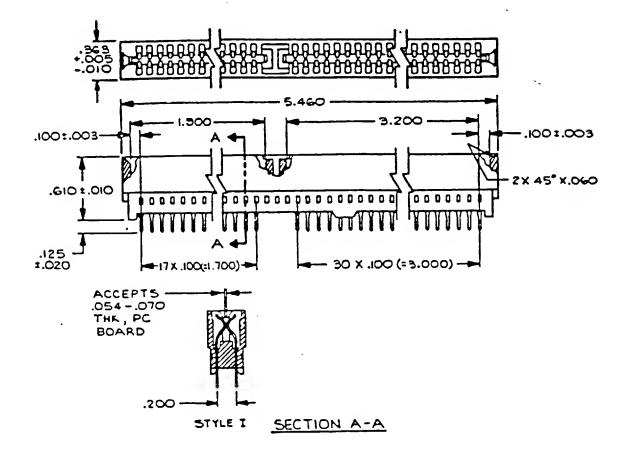

| 11.1 ADD-ON CARD CONNECTOR-SET SPECIFICATION               | 68  |

|                                                            | 71  |

| 12.1 DEPTH & SIZE                                          | 71  |

| 12.2 SPACING & THICKNESS                                   | 73  |

.

.

. •

•

# Page 4 INTEL ISA Bus Specification and Application Notes

•

## TABLE OF FIGURES

| TABLE OF FIGURES          |      |      |     |     |   |     |     |   |   |   |     |   |   |   |    |

|---------------------------|------|------|-----|-----|---|-----|-----|---|---|---|-----|---|---|---|----|

| 4.0 PLATFORM ARCHITECTUR  | Е.   |      |     |     |   |     |     |   |   |   |     |   |   |   |    |

| 6.4.1 BYTE SWAPPER HARDW  | ARE  |      | •   | • • | • |     | •   | • | • | • | •`` | • | • | • | 27 |

| 6.4.2 BYTE SWAPPER HARDW. | ARE  |      | •   | • • | • |     | •   | • | • | • | •   | • | • | • | 27 |

| 7.1.1 INPUT ADDRESS CIRC  |      |      |     |     |   |     |     |   |   |   |     |   |   |   |    |

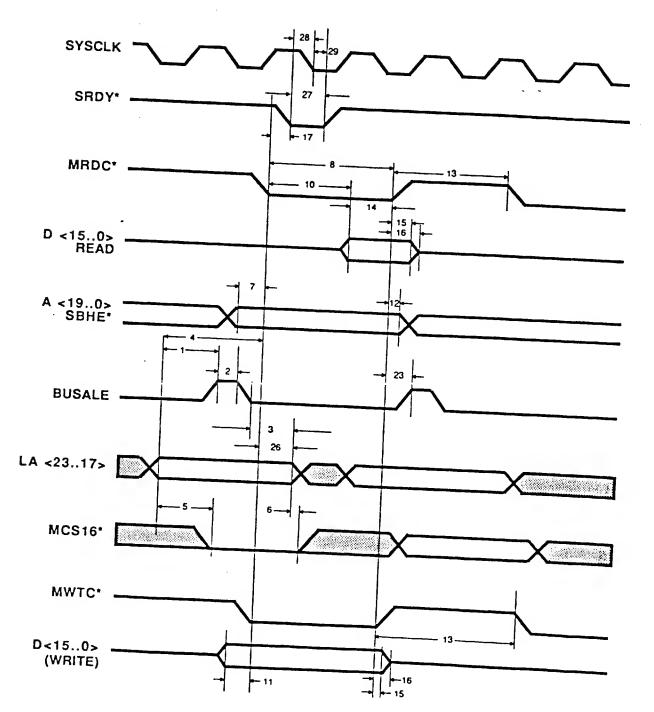

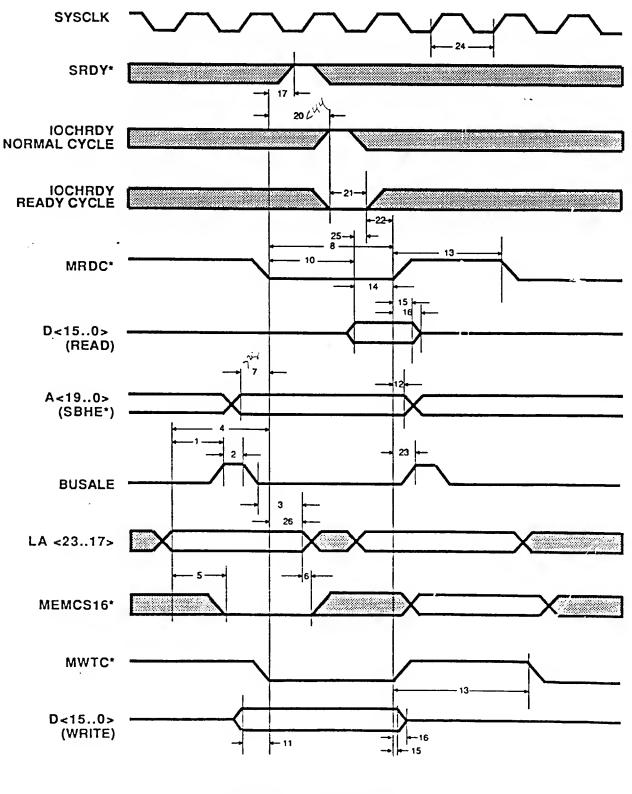

| 8.1.1 16-BIT MEMORY READ  | & W. | RITE | CY  | CLE |   |     |     | • | • | • | •   | • | • | • | 43 |

| 8.1.2 16-BIT MEMORY READ  | & W. | RITE | CY  | CLE |   |     |     | • | • | • |     | • |   | • | 44 |

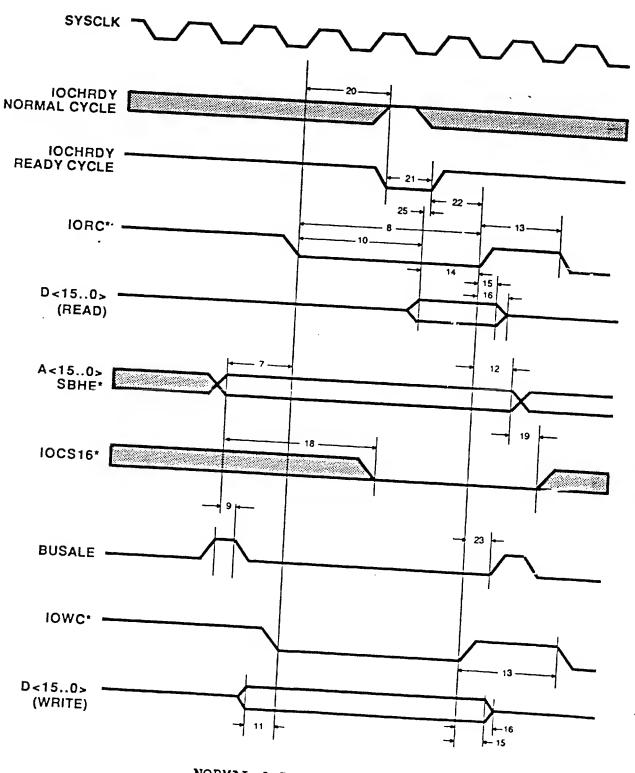

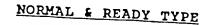

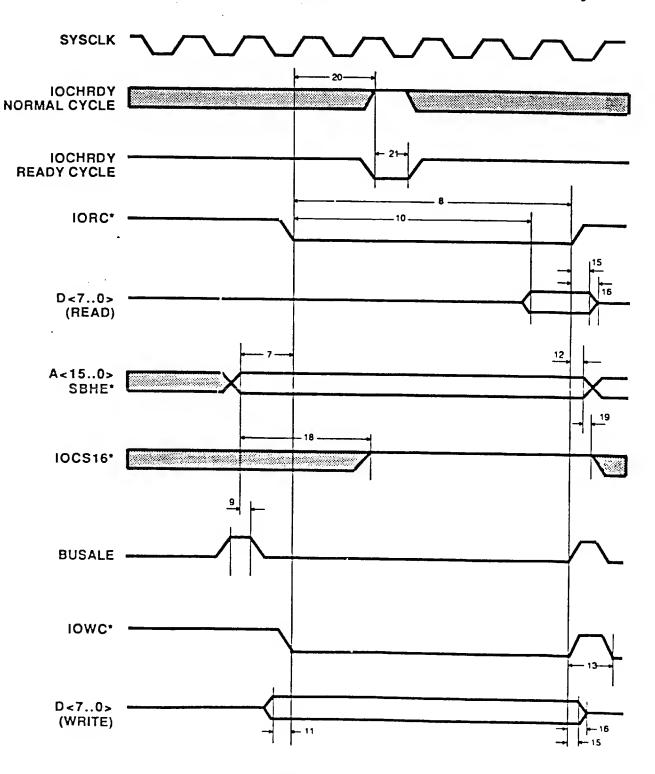

| 8.1.3 16-BIT I/O READ &   | WRIT | E CY | CLE | s.  | • |     | •   | • | • |   | •   | • | • | • | 45 |

| 8.1.4 8-BIT MEMORY READ   | & WR | ITE  | CYC | LE  | • | • • | •   |   |   | • | •   | • | • | • | 46 |

| 8.1.5 8-BIT I/O READ & W  | RITE | CYC  | LE  |     | • |     |     | • |   |   |     | • | • |   | 47 |

| 8.2 NORMAL & READY TYPE   | REFR | ESH  | CYC | LE  |   |     |     | • | • | • | •   |   | • |   | 50 |

| 8.3 DMA TRANSFER CYCLES   |      | • •  |     |     | • |     |     |   |   |   |     |   |   |   | 53 |

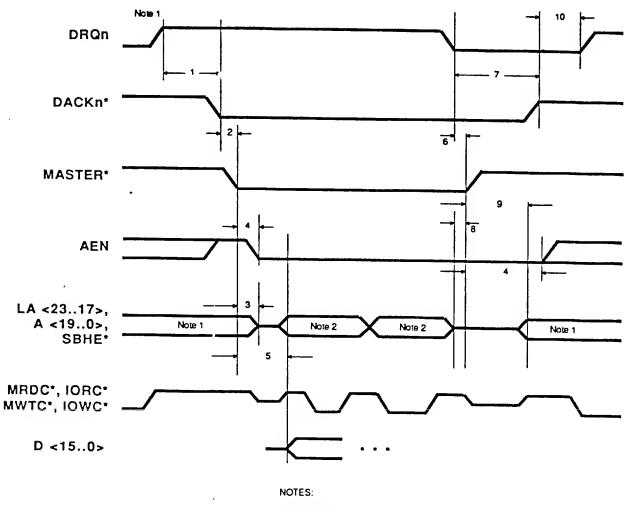

| 8.4 BUS OWNERSHIP CYCLES  |      |      |     |     |   |     |     |   |   |   |     |   |   |   | 55 |

| 11.1.0 98-PIN CONNECTOR   |      |      |     |     |   |     |     | - |   | - |     |   |   |   | 69 |

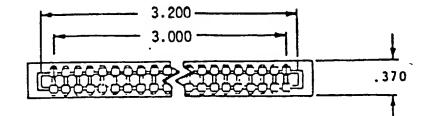

| 11.1.1 62-PIN CONNECTOR   |      |      |     |     |   |     |     |   |   |   |     |   |   |   |    |

| 12.0 MAXIMALLY-SIZED AND  |      |      |     |     |   |     |     |   |   |   |     |   |   |   |    |

|                           |      |      |     |     |   |     | • • | • | • | • | •   | • | • | • |    |

## TABLE OF TABLES

| 5.1   | PRIMAR  | Y CPU | J IS       | BUS   | OW  | NE: | R   | •  | •   | •  | •  | •  | •      | • | •  | • | ٠ | • | • | •   | • | • | • | 12 |

|-------|---------|-------|------------|-------|-----|-----|-----|----|-----|----|----|----|--------|---|----|---|---|---|---|-----|---|---|---|----|

| 5.2   | DMA COI | NTROL | LER        | IS 1  | BUS | 0   | WN. | ER |     | •  | •  | •  | •      | • | •  | • | • | • |   | •   | • | • | • | 14 |

| 5.3   | ADD-ON  | CARE  | ) ACC      | ESS   | PL  | AT  | FO  | RM | 0   | R  | AD | D- | ON     | C | AF | D | • | • | • | ••. | • | • | • | 17 |

| 5.4.1 | REFR    | ESH C | ONTF       | SOLLI | ER  | IS  | B   | US | 0   | WN | ER |    | •      | • | •  | • | • | • |   | •   | • | • | • | 22 |

| 5.4.2 |         | ON CA | RD 1       | IS BU | JS  | OW  | NE. | R  | •   | •  | •  | •  | •      | • | •  | • | • | • | • | •   | • |   | • | 23 |

| 6.4.1 |         | S SWA | PPEL       | ) FOI | RA  | N.  | AC  | CE | SS  | С  | YC | LE | t<br>1 | • | •  | • | • | • |   |     |   |   |   | 28 |

| 6.4.2 |         | 5 SWA | <b>PPE</b> | ) FOI | RA  | T   | RA  | NS | FE. | R  | СҮ | CL | E      | • |    |   |   |   | • |     | • | • |   | 28 |

| 7.1.6 | MAXII   | MUM C | URRE       | ENT   | •   | •   | •   | •  | •   | •  | •  | •  | •      | • | •  |   |   | • | • |     |   |   |   | 39 |

| 9.0.1 | 0 WA    | IT SI | ATE,       | NOI   | RMA | L,  | &   | R  | EA  | DY | •  |    | •      | • |    |   |   |   |   |     |   |   |   | 56 |

| 9.0.2 | REFR    | ESH C | YCLE       | ES .  | •   | •   |     |    |     | •  | •  |    | •      |   |    |   |   |   |   |     |   |   |   | 59 |

| 9.0.3 | DMA     | CYCLE | cs .       |       | ,   |     | •   | •  | •   |    |    |    |        |   |    |   |   |   |   |     |   | • | • | 60 |

| 9.0.4 | BUS     | OWNEF | SHIE       | CYC   | CLE | S   |     | •  |     |    |    |    |        |   |    |   |   |   |   |     |   |   |   | 61 |

| 10.1. | 0 PIN   | ASSI  | GNME       | ENTS  | •   | •   | •   | •  |     |    | •  |    |        |   |    |   |   |   |   | •   |   | • | • | 62 |

| 10.1. | 1 PIN   | ASSI  | GNME       | ENTS  |     |     |     |    |     |    | _  |    |        |   |    |   |   |   |   |     |   | • | • | 63 |

| 10.3  | VOLTA   | GE &  | CURF       | RENT  |     |     |     |    |     |    |    |    |        |   |    |   | Ţ |   |   |     |   | • | • | 65 |

| 10.5  | BACKP   | LANE  | RESI       | ISTO  | RS  |     |     | -  | -   | -  | -  |    | •      | - | •  | • | • | • | • | •   | • | • | • | 67 |

|       |         |       |            |       |     | -   | •   | -  | -   | -  | •  | •  | •      | • | •  | • | • | • | • | •   | • | • | • | 07 |

#### 1.0 SCOPE

The Intel ISA bus is a parallel bus derived from the IBM PC/AT memory and I/O bus. This document supplies the electrical and mechanical specifications for the Intel ISA bus as implemented at the connectors of ISA compatible platform products supplied by the Intel OEM Platforms organization. This document also describes the bus interface, connector pin-out, and electrical interface to standard IBM PC/AT<sup>1</sup> cards.

The main focus is to provide application information for our customers to successfully design add-on cards for Intel ISA-based platforms. The task of assembling this specification is difficult in that thousands of add-on cards have been designed without the benefit of a document of this nature. The details in this document represent the accumulation of timings, platform architecture, and good design practices developed during the design of a variety of Intel board products. There is no guarantee that an add-on card compliant to this document will work in any or all Intel or non-Intel ISA platform products. Newly developed add-on cards must be validated with a variety of actual ISA-based platforms.

Any questions, comments, or clarifications would be appreciated and can be addressed to:

Intel, OEM Platforms Operation Technical Marketing, HF1-60 5200 N.E. Elam Young Parkway Hillsboro, Oregon 97124

#### 2.0 NATURE OF THIS SPECIFICATION

· ·

This specification applies to all Intel ISA bus platforms. It specifically contains application information to aid in the design of add-on cards. Any differences between this specification and the ISA bus implementation of a specific Intel baseboard must be reviewed in the hardware reference manual of the product.

Three unique headings are used to draw attention to important information. These headings are:

| NOTE    | Special informa<br>consideration. | tion worthy of                     |

|---------|-----------------------------------|------------------------------------|

| CAUTION |                                   | can cause fatal<br>if not properly |

<sup>&</sup>lt;sup>1</sup>PC/AT, PC/XT, and IBM are trademarks of International Business Machines Corporation.

#### considered.

| ADD-ON | CARD  | Usefu | al informat | tior | 1 to con | sider |

|--------|-------|-------|-------------|------|----------|-------|

| DESIGN | FOCUS | when  | designing   | an   | add-on   | card. |

#### 3.0 CONVENTIONS

Throughout this specification, an asterisk (\*) following a signal name indicates that the signal is in its logically true state when its voltage level is in the low state. A signal name that is not followed by an asterisk indicates that the signal is in its logically true state when its voltage level is in the high state.

To avoid confusion when referring to the logical state of signals, the terms "enabled" and "disabled" are used throughout this document. A signal is said to be enabled when it is logically true, and it is said to be disabled when it is logically false.

Many signals on the Intel ISA bus are more easily or conveniently discussed as a group, since there are many signals with identical functionality. Names for signals within these groups follow a decimal radix numbering convention, as follows.

- (1) When discussed as an individual signal, the decimal number is simply appended to the signal name, e.g., A15.

- (2) A disjoint set of signal lines with the same signal group may be collectively referenced by listing the group name and appending the decimal numbers within brackets, e.g., A<15,12,03>.

- (3) A range of consecutive signals within the same group may be referenced by listing the group name and appending the beginning and ending signals, separated by double periods, e.g., A<15..08>. Ranges of signals include the beginning and ending signals in the range.

- (4) Consecutive and disjoint signals within the same group are referenced by using a combination of both methods (2) and (3), e.g., A<15,07..00>.

- (5) A signal group name with nothing appended to it refers to the entire signal group, e.g., A is equivalent to A<15..00>.

A set of brackets "[]" are used to indicate the connector size. [8] is an 8-bit resource and [8/16] supports an 8- or 16-bit resource.

Signal lines and groups of signal lines on the Intel ISA bus are always shown in bold capital letters, as in the case of the individual signal "MEMREF\*".

· ·

The use of the word "bit" always refers to singular or plural to data bits unless the adjective "address" precedes it.

#### 4.0 ARCHITECTURE OVERVIEW

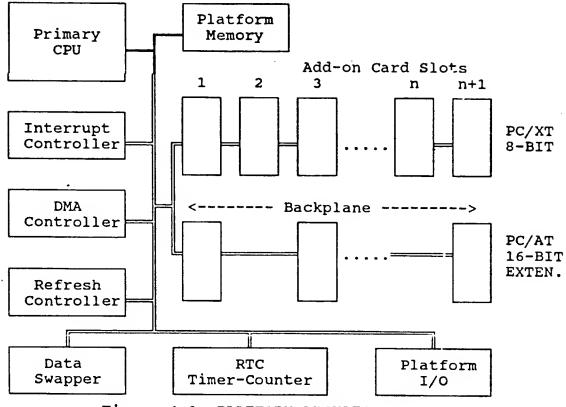

The Intel ISA bus is part of a the Intel ISA compatible platform architecture. The resources of this architecture that interact with the ISA bus are the Primary CPU, DMA Controller, Interrupt Controller, Refresh Controller, Memory, Byte Swapper, add-on cards, RTC/Timer-counter, and I/O resources (See Figure 4.0). The Primary CPU, DMA Controller, Refresh Controller and add-on cards are the only resources that can become bus owners and are defined as follows:

| <b>Primary</b> | СЪЛ | A CPU that resides on the ISA<br>compatible platform and is the<br>default bus owner. The DMA and<br>Refresh Controllers disable this<br>resource to obtain bus ownership.<br>The Primary CPU also responds to<br>interrupt requests via the Interrupt<br>Controller. |

|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |     |                                                                                                                                                                                                                                                                       |

- DMA Controller This resource is connected to the DMA request and acknowledge lines. An active DMA request will enable this resource to become the bus owner and transfer data between memory and I/O resources on the platform.

- Add-on Cards A resource that is attached to the platform via the ISA bus connectors. Add-on cards can become bus owners, memory or I/O access resources, or participate in memory or I/O DMA transfers.

Refresh Controller The Refresh Controller becomes bus owner and generates an address and read pulse to refresh DRAM resources on the platform or add-on card.

Other resources cannot become bus owners but are essential in maintaining IBM/AT compatibility. These resources are defined as follows: (See Figure 4.0)

RTC / Timer-counter

. ×

This resource consists of the real time clock (RTC) for the date and time, and an Intel 8254A. One of the

Page 9

timer-counters is used to generate a pulse every 15 usec. to trigger the Refresh Controller to do a refresh cycle.

Backplane The portion of the platform that interconnects the connectors with other platform resources.

PlatformSome or all of the random accessMemorymemory devices (RAM) are on the<br/>platform proper (Platform Memory).<br/>Other RAM resources may reside on the<br/>add-on cards.

- PlatformSome or all of the I/O resourcesI/O(like serial and parallel ports) can<br/>reside on the platform. The<br/>remainder of the I/O resources can<br/>reside on the add-on cards.

- Interrupt Controller This resource is connected to the interrupt request lines of the bus and requests service from the Primary CPU. The Interrupt Controller is the Intel 8259A.

- Data Swapper This resource allows 8- and 16-bit resources to interact.

Figure 4.0 PLATFORM ARCHITECTURE

The Intel ISA bus is the combination of the aforementioned backplane and connectors that interconnect add-on card slots and platform resources. The add-on card slots can support either 8or 16-bit add-on cards. The [8] slot contains a single connector; the [8/16] has one additional connector. The single connector slot can support only eight data bits. The double connector slot can support either 8 or 16 data bits. The total number of slots is limited to load and transmission line issues, however most implementations have eight slots due to the available DMA channels and interrupt lines.

#### 5.0 BUS OWNER ATTRIBUTES AND DESIGN

· ·

#### 5.1 PRIMARY CPU

The Primary CPU is the default bus owner. The Refresh and DMA Controllers (and the add-on cards by subletting from the DMA Controller) become bus owners only after disabling it. The disabling of the Primary CPU is accomplished by a handshake of its hold request and hold acknowledge lines by the DMA or Refresh Page Missing From Original Document

Table 5.1 outlines which signal line resources are driving or receiving when the Primary CPU is bus owner. It also specifies the type of driver.

| LINE     |     | ADD        |     |   | EIVER<br>Mem |     | DRIVER<br>TYPE |

|----------|-----|------------|-----|---|--------------|-----|----------------|

| AEN      | -   | R          | D   |   |              | R   | TTL            |

| BUSALE   | D   | R          | -   |   | R            | R   | TTL            |

| DACK#*   | -   | R          | D   | - | -            | R   | TTL            |

| DRQ# (1) | -   | D          | R   |   |              | D   | TTL            |

| IOCHCK*  | R   | D          | -   |   | D            | D   | oc             |

| IOCHRDY  | R   | D          | -   | - | D            | D   | oc             |

| IOCS16*  | R   | D          | -   | - | -            | D   | oc             |

| IORC*    | D   | R          | -   | - | -            | R   | TRI            |

| IOWC*    | D   | R          | -   | - | -            | R   | TRI            |

| IRQ# (2) | R   | D          |     | - | -            | D   | TTL            |

| LA#      | D   | R          | ••• | - | R            | -   | TRI            |

| SECMAST* | -   | -          | •-  | - | -            | -   | oc             |

| MCS16*   | R   | D          | -   | - | D            | -   | oc             |

| MRDC*    | D   | R          | •   | - | R            | -   | TRI            |

| MWTC*    | D   | R          |     | - | R            | -   | TRI            |

| 840SC    | D   | R          | -   | - | -            | -   | TTL            |

| MEMREF*  | -   | -          | -   | - | -            |     | oc             |

| RSTDE(3) | D   | R          | R   | - |              | R   | TTL            |

| A#       | D   | R          | -   | - | R            | R   | TRI            |

| SBHE#(4) | D   | R          | -   | - | R            | R   | TRI            |

| D#       | D/R | D/R        | -   | - | D/R          | D'U | TRI            |

| MEMR*    | (5) | R          | -   | - | R            | -   | TRI            |

| MEMW*    | (5) | R          | -   | - | R            | -   | TRI            |

| SYSCLK   | D   | R          | R   | - | R            | -   | TRI            |

| TC       | - 1 | <b>-</b> ' | -   | - | -            | -   | TTL            |

| SRDY*    | R   | D          | -   | - | D            | -   | oc             |

Table 5.1 PRIMARY CPU JS BUS OWNER

NOTE: Primary CPU = PRI, Add-on card = ADD, DMA Controller = DMA, Refresh Controller = REF, Platform memory = MEM, Platform I/O = I/O, TTL = "ALS" or "LS", Open collector = OC, and Tristatable drivers/receivers = TRI.

"-" indicates that the respective signal line is not enabled or sensed by the resource.

"X" indicates a "don't care" condition. A resource can enable the signal, but it will be ignored by other resources.

(1) DRQ# can be driven but will not be acted upon until the DMA Controller is bus owner.

•

Page 13

- (2) Received by the Primary CPU via the Interrupt Controller and acted upon at the discretion of the Primary CPU when it is bus owner.

- (3) This signal must be sensed at all times and immediately acted upon if enabled.

- (4) Always received by the byte swapper hardware.

- (5) Driven by platform resources, the address is in the first 1MB of the address and either MRDC\* or MWTC\* signal lines.

#### 5.2 DMA CONTROLLER

The DMA lines of the connector are directly attached to the Intel 8237A DMA Controller. When the DMA request lines are driven by a resource, the DMA Controller obtains bus ownership by handshaking the hold request and hold acknowledge lines of the Primary CPU. Once bus ownership is granted, the associated DMA acknowledge line is driven and the DMA transfer cycle begins. When the DMA acknowledge line is attached to an add-on card, the DMA transfer cycles will not begin if the SECMAST\* line is enabled by the addon card (See Section 5.4 for more information).

The I/O resources involved in a DMA transfer must match in data size of the DMA channel. DMA channels 0-3 only support 8-bit I/O resources; all data must be transferred as data bits on the data lines D<07..00>. Byte swapping hardware on the platform will use A0 and SBHE\* to port the high byte for 16-bit memory to the low byte of the 8-bit I/O resource when needed. DMA channels 5-7 only support 16-bit I/O resources; all data must be transferred as 16 data bits on data lines D<15..00>. The memory involved with the transfer must have a data size of 16 bits; the platform byte swapping hardware will not compensate for data size mismatch.

NOTE

An 8-bit memory resource can only be part of a DMA transfer with an 8-bit I/O resource; the use of 3-bit memory resource with a 16-bit I/O resource is not allowed.

#### CAUTION

The Refresh Controller cannot become bus owner when the DMA Controller is bus owner. Thus, continuous bus ownership by the DMA Controller for transfers longer than 15 usec. may cause data to be lost in resources that have dynamic RAM and rely on ISA bus refresh cycles.

• •

#### ADD-ON CARD DESIGN FOCUS

DMA request and acknowledge lines are driven by the TTL drivers, and are attached to all the slots. The add-on cards must allow the selection of different DMA channels at the time of installation to avoid conflict with already installed cards or platform resources.

The add-on cards can only be in the DMA memory or I/O modes when interacting with the DMA Controller as a DMA resource. See Section 5.3.

Table 5.2 outlines which signal lines the platform resources are driving receiving when the DMA Controller is bus owner. It also specifies the type of driver.

| LINE     |     |     |   |   | EIVEF<br>Mem |     | DRIVER<br>TYPE |

|----------|-----|-----|---|---|--------------|-----|----------------|

| AEN      | _   | R   | D | _ | _            | R   | TTL            |

| BUSALE   | (6) | R   | _ | - | R            | R   | TTL            |

| DACK#*   | _   | R   | D | - | -            | R   | TTL            |

| DRQ# (1) | -   | D   | R | - | -            | D   | TTL            |

| IOCHCK*  | R   | D   | - | - | D            | D   | oc             |

| IOCHRDY  | -   | D   | R | - | D            | D   | oc             |

| IOCS16*  | -   | х   | х | - | -            | х   | oc             |

| IORC*    | -   | R   | D | - | -            | R   | TRI            |

| IOWC*    | -   | R   | D | - | -            | R   | TRI            |

| IRQ#(2)  | R   | D   | - | - | -            | D   | TTL            |

| LA#      | -   | R   | D | - | R            | -   | TRI            |

| SECMAST* | -   | -   | - | - | -            | - 1 | oc             |

| MCS16*   | -   | х   | х | - | Х            | -   | OC             |

| MRDC*    | -   | R   | D | - | R            | -   | TRI            |

| MWTC*    | -   | R   | D | - | R            | -   | TRI            |

| 840SC    | D   | R   | - | - | -            | -   | TTL            |

| MEMREF*  | -   | -   | - | - | -            | -   | oc             |

| RSTDE(3) | D   | R   | R | - | -            | R   | TTL            |

| A#       | -   | R   | D | - | R            | R   | TRI            |

| SBHE#(4) | -   | R   | D | - | R            | -   | TRI            |

| D#       | -   | D/R | - | - | D/R          | D/R | TRI            |

| MEMR*    | (5) | R   | - | - | R            | -   | TRI            |

| MEMW*    | (5) | R   | - | - | R            | -   | TRI            |

| SYSCLK   | D   | R   | R | - | R            | -   | TRI            |

| TC       | -   | R   | D | - | -            | R   | TTL            |

| SRDY*    | -   | -   | - | - | -            | -   | oc             |

Table 5.2 DMA CONTROLLER IS BUS OWNER

• ·

NOTE: Primary CPU = PRI, Add-on card = ADD, DMA Controller = DMA, Refresh Controller = REF, Platform memory = MEM, Platform I/O = I/O, TTL = "ALS" or "LS", Open collector = OC, and Tristatable drivers/receivers = TRI.

"-" indicates that the respective signal line is not enabled or sensed by the resource.

"X" indicates a "don't care" condition. A resource can enable the signal, but it will be ignored by other resources.

- (1) DRQ% can be driven but will not be acted upon until the DMA Controller is bus owner.

- (2) Received by the Primary CPU via the Interrupt Controller and acted upon at the discretion of the Primary CPU when it is bus owner.

- (3) This signal must be sensed at all times and immediately acted upon if enabled.

- (4) Always received by the byte swapper hardware.

- (5) Driven by platform resources, the address is in the first 1MB of the address and either MRDC\* or MWTC\* signal lines.

- (6) Driven to the enabled level by platform hardware for the entire cycle.

#### 5.3 ADD-ON CARDS

Add-on cards can operate in five different modes: bus owner, DMA memory or I/O, access memory or I/O resource, refresh, or reset. Add-on cards can support any combination of the first four modes, but all add-on cards must comply with the reset mode.

BUS OWNER MODE

Only add-on cards of 16-bit data size plugged into an [8/16] slot can become a bus owner. The add-on card becomes bus owner by driving a DRQ\* and the SECMAST\* line once the associated DACK line is driven by the DMA Controller. The add-on cards can begin ISA bus access cycles as 8- or 16-bit. The completion of the cycle as 16-bits is also dependent on the state of MCS16\* and IOCS16\* as driven by accessed resources.

The cycles executed by the add-on card are all access cycles. The add-on card cannot execute DMA transfer cycles because all of the DMA control lines are attached to the platform DMA Controller and can't be shared by DMA Controllers if one resides on the add-on card. When an add-on card is bus owner, the DMA Controller disables the AEN line when it sublets bus ownership. Disabling the AEN line allows I/O resources to decode the address lines and be accessed by the add-on card. With AEN disabled, no DMA transfers can occur. (See AEN description in Section 7.1.) Also, DMA transfer cycles cannot be executed because the DMA Controller has

· ·

the channel that granted bus ownership active; the other DMA channels can't be activated until the channel involved with add-on card bus ownership is no longer active.

NOTE

Software supplied with the add-on card must instruct the Primary CPU to program a specific DMA channel in the cascade mode. The DMA channel must be programmed into the cascade mode in order for the associated add-on card to become bus owner.

#### NOTE

If the add-on card begins an access as 16-bit in size, and MCS16\* or IOCS16\* is not enabled, then the cycle is completed as 8-bits. The platform byte swapper will port the 8-bit byte between D<15..08> and D<07..00> as determined by SBHE\* and A0.

If the add-on card begins an access as 8-bit in size, then the platform must support the appropriate byte swapping. Traditionally not all platforms have supported 8-bit add-on cards as bus owners. Please refer to the technical reference manual for the platform.

See Section 6.4 for more information.

#### CAUTION

Page 16

The add-on card that becomes bus owner must drive the MEMREF\* line every 15 usec. to request the Refresh Controller to execute a refresh cycle. The Refresh Controller actually executes the cycle by driving the address lines, command lines, and monitoring the IOCHRDY line, but the add-on card drives the MEMREF\* line and retains bus ownership.

The add-on card must be responsible for requesting the refresh cycle because the Refresh Controller can't become bus owner if the DMA Controller is the bus owner. Recall that the add-on card becomes bus owner by subletting from the DMA Controller which is active and indirectly bus owner.

Table 5.3 outlines which signal lines the platform resources are driving receiving a signal when the add-on card is bus owner. It also specifies the type of driver.

| LINE     |            | DRIVE:<br>ADDX |     |   | EIVE:<br>REF | rs<br>Mem | 1/0 | DRIVER<br>TYPE |

|----------|------------|----------------|-----|---|--------------|-----------|-----|----------------|

|          |            |                |     |   |              |           |     |                |

| AEN      | -          | -              | R   | D | -            | -         | R   | TTL            |

| BUSALE   | (6)        | -              | R   | - | -            | R         | R   | TTL            |

| DACK#*   | -          | R              | R   | D | -            | -         | R   | TTL            |

| DRQ# (1) | -          | D              | -   | D | -            | -         | D   | TTL            |

| IOCHCK*  | R          | D              | D   | - | -            | D         | D   | oc             |

| IOCHRDY  | -          | R              | D   | - | -            | D         | D   | oc             |

| IOCS16*  | -          | R              | D   | - | -            | -         | D   | oc             |

| IORC*    | -          | D              | R   | - | -            | -         | R   | TRI            |

| IOWC*    | -          | D              | R   | - | -            | -         | R   | TRI            |

| IRQ# (2) | R          | D              | D   | - | -            | -         | D   | TTL            |

| LA#      | -          | D              | R   | - | -            | R         | -   | TRI            |

| SECMAST* | -          | D              | -   | R | -            | -         | -   | oc             |

| MCS16*   |            | R              | D   | - | -            | D         | -   | oc             |

| MRDC*    | <b>-</b> . | D              | R   | - | -            | R         | -   | TRI            |

| MWTC*    | -          | D              | R   |   | -            | R         | -   | TRI            |

| 840SC    | D          | R              | R   | - | -            | -         | -   | TTL            |

| MEMREF*  | -          | -              | -   | - | -            | -         | -   | oc             |

| RSTDE(3) | D          | R              | R   | R | -            | -         | R   | TTL            |

| SA#      | -          | D              | R   | - | -            | R         | R   | TRI            |

| SBHE#(4) | . –        | D              | R   | - | -            | -         | -   | TRI            |

| SD#      | -          | D/R            | D/R | - | -            | D/R       | D/R | TRI            |

| MEMR*    | (5)        | -              | R   | - | -            | R         | _   | TRI            |

| MEMW*    | (5)        | -              | R   | - | -            | R         | _   | TRI            |

| SYSCLK   | D          | R              | R   | R | -            | R         | R   | TRI            |

| TC       | -          | -              | -   | - | -            | -         | -   | TTL            |

| SRDY*    | -          | -              | -   | - | -            | -         | -   | oc             |

Table 5.3ADD-ON CARD ACCESS PLATFORM OR ADD-ON CARDMEMORY OR I/OADD-ON CARD (ADDX) IS BUS OWNER

NOTE: Primary CPU = PRI, Add-on card = ADD, DMA Controller = DMA, Refresh Controller = REF, Platform memory = MEM, Platform I/O = I/O, TTL = "ALS" or "LS", Open collector = OC, and Tristatable drivers/receivers = TRI.

, ·

"-" indicates that the respective signal line is not enabled or sensed by the resource.

"X" indicates a "don't care" condition. A resource can enable the signal but it will be ignored by other

.

-

resources.

- (1) DRQ# can be driven but will not be acted upon until the DMA Controller is bus owner.

- (2) Received by the Primary CPU via the Interrupt Controller and acted upon at the discretion of the Primary CPU when it is bus owner.

- (3) This signal must be sensed at all times and immediately acted upon if enabled.

- (4) Always received by the byte swapper hardware.

• •

- (5) Driven by platform resources, the address is in the first 1MB of the address and either MRDC\* or MWTC\* signal lines.

- (6) Driven to the enabled level by platform hardware for the entire cycle.

DMA MEMORY OR I/O MODES

The add-on card can only be in the DMA modes when the DMA Controller is bus owner. The DMA memory mode allows data to transfer between other I/O resources and the add-on card's memory. The DMA I/O mode allows data to transfer between memory and add-on card's I/O by handshaking the DMA request and DMA acknowledge lines. The add-on card that responds as an 8-bit or 16-bit I/O resource must use the 8- and 16-bit DMA channels, respectively. An add-on card can support both memory and I/O modes at once, which would transfer data between add-on card memory and I/O.

The condition of the add-on card signal lines when the DMA Controller is bus owner is outlined in Table 5.2.

Page 18

Page 19

#### CAUTION

There are special considerations when the DMA Controller is executing a transfer cycle between an 8-bit I/O resource and a 16bit add-on card memory resource. First, the add-on card knows that the transfer is with an 8-bit I/O resource because of BBHE\* and AO. Second, when memory is being written, the platform byte swapper hardware will place the byte either on D<15..08> or D<07..00>; the add-on card must monitor BBHE\* and AO to determine which data lines contain the correct byte. Third, when memory is being read, the platform byte swapper will port the byte from D<15..08> to D<07..00> when appropriate. The add-on card must monito: BBHE\* and AO to determine when it must tristate D<07..00> to prevent buffer fights.

The add-on card can be a 16-bit memory resource in a DMA transfer for I/O resources of either 8- or 16-bit data size. The add-on card can be an 8-bit memory resource in a DMA transfer only if the I/O resource is 8-bits.

Another consideration is a DMA transfer cycle that writes a memory resource when an add-on card is the 8-bit I/O resource of the transfer. If the add-on card is installed in an [8/16] slot, then it must tristate the D<15..08> lines. These lines must be tristated to prevent buffer fights with the platform byte swapper when it is porting the low byte to the high byte during the transfer cycle.

See Section 6.4 for further information.

CAUTION

When the DMA Controller is bus owner it ignores the SRDY\* signal; thus the add-on card cannot implement fast RAM DMA transfers.

#### ACCESS MEMORY OR I/O MODE

The add-on card can appear simply as a memory or I/O resource when the Primary CPU or another add-on card is bus owner.

#### CAUTION

There are special considerations when an add-on card resides in an [8/16] slot and responds as an 8-bit memory or I/O resource during an access cycle. When the add-on card resource is being read, the platform byte swapper hardware will place the byte either on D<15..08> or D<07..00> to support the 16-bit data size of the bus owner. The add-on card must tristate D<15..08> because these lines will be driven by the platform byte swapper hardware.

See Section 6.4 for further information.

#### CAUTION

When some add-on cards are bus owners they ignore the IOCHRDY or SRDY\* signals and run a default 8-bit or 16-bit memory cycle. Any add-on card that returns IOCHRDY or SRDY\* signals to an add-on card as it does with a Primary CPU must determine if the accessing addon card can support these lines.

Tables 5.1 and 5.3 outline which signal lines the platform resources are driving or receiving when an add-on card is in the access memory or I/O mode and the Primary CPU or another add-on card (noted as ADDX) are bus owners, respectively. It also specifies the type of driver.

#### RESET MODE

The add-on card enters the reset mode whenever the RSTDEV is enabled, independent of what other mode it is in. All of the addon card bus tristatable signals must be tristated and all open collector signals must be disabled within 500ns of RSTDEV being enabled. The board must complete its initialization within one millisecond of the RSTDEV being enabled and be ready for normal bus operations. Normal bus operations commence immediately when the RSTDEV signal line is disabled.

#### 5.4 REFRESH CONTROLLER

The Refresh Controller executes a read cycle at a specific address to refresh the platform or add-on cards' DRAM. Every 15 usec. the Refresh Controller tries to obtain bus ownership in order to run a refresh cycle. If the present bus owner is the Primary CPU, then bus ownership is transferred to the Refresh Controller. If the present bus owner is an add-on card, then the Refresh Controller will execute a refresh cycle only when the add-on card enables the MEMREF\* line. If the DMA Controller is the bus owner, then no refresh cycles can be executed until the DMA Controller

es Page 21

relinquishes bus ownership.

When a refresh cycle is executed, the Refresh Controller drives address line A<07..00> with one of the possible 256 refresh addresses. The other address lines are undefined and should be tristated by resources that can drive them. The cycle is essentially a normal or ready type access cycle with both MEMR\* and MRDC\* enabled.

CAUTION

The refresh cycle must be executed every 15 microseconds to ensure that all DRAM addresses are accessed every 4 milliseconds. If this does not occur, DRAM data may be lost. Tables 5.4.1 and 5.4.2 outline which signal lines the platform resources are driving and receiving a signal for a refresh cycle when the Refresh Controller and add-on card are bus owners, respectively. It also specifies the type of driver.

| LINE     |     |   | RS &<br>DMA |   | eivei<br>Mem |   | DRIVER<br>Type |

|----------|-----|---|-------------|---|--------------|---|----------------|

| AEN      | _   | x | x           | - | -            | x | TTL            |

| BUSALE   | (6) | R | -           | - | R            | R | TTL            |

| DACK#*   | -   | R | D           | - | -            | R | TTL            |

| DRQ#-(1) | -   | D | R           | - | -            | D | TTL            |

| IOCHCK*  | R   | D | -           | - | D            | D | oc             |

| IOCHRDY  | -   | D | -           | R | D            | D | oc             |

| IOCS16*  | Х   | х | х           | х | Х            | Х | oc             |

| IORC*    | -   | - | -           | - | -            | - | TRI            |

| IOWC*    | -   | - | -           | - | -            | - | TRI            |

| IRQ# (2) | R   | D | -           | - | -            | D | TTL            |

| LA#      | -   | - | -           | - | . –          | - | TRI            |

| SECMAST* | -   | - | -           | - | -            | - | oc             |

| MCS16*   | Х   | х | х           | Х | Х            | Х | oc             |

| MRDC*    | -   | R | -           | D | R            | - | TRI            |

| MWTC*    | -   | - | -           | - | -            | - | TRI            |

| 840SC    | D   | R | -           | - | -            | - | TTL            |

| MEMREF*  | -   | R | -           | D | R            | - | oc             |

| RSTDE(3) | D   | R | R           | - | -            | R | TTL            |

| A        |     |   |             |   |              |   |                |

| <0700>   | -   | R | -           | D | R            | R | TRI            |

| <1908>   | -   | - | -           | - | -            | - | TRI            |

| SBHE#(4) | -   | - |             |   | -            | - | TRI            |

| D#       | -   | - | -           | - | -            | - | TRI            |

| MEMR*    | (5) | R | -           | - | R            | - | TRI            |

| MEMW*    | -   | - | -           | - | -            | - | TRI            |

| SYSCLK   | D   | R | R           | - | R            | - | TRI            |

| тс       | -   | - | -           | - | -            | - | TTL            |

| SRDY*    | -   | - | -           | - | -            | - | oc             |

Table 5.4.1 REFRESH CONTROLLER IS BUS OWNER

NOTE: Primary CPU = PRI, Add-on card = ADD, DMA Controller = DMA, Refresh Controller = REF, Platform memory = MEM, Platform I/O = I/O, TTL = "ALS" or "LS", Open collector = OC, and Tristatable drivers/receivers = TRI.

۰.

"-" indicates that the respective signal line is not enabled or sensed by the resource.

"X" indicates a "don't care" condition. A resource can

Page 22

Page 23

enable the signal but it will be ignored by other resources.

- (1) DRQ# can be driven but will not be acted upon until the DMA Controller is bus owner.

- (2) Received by the Primary CPU via the Interrupt Controller and acted upon at the discretion of the Primary CPU when it is bus owner.

- (3) This signal must be sensed at all times and immediately acted upon if enabled.

- (4) Always received by the byte swapper hardware.

- (5) Driven by platform resources, the address is in the first 1MB of the address and either MRDC\* or MWTC\* signal lines.

- (6) Driven to the enabled level by platform hardware for the entire cycle.

| LINE     |         | ADD |      |       | EIVE<br>Mem |       | DRIVER<br>TYPE |

|----------|---------|-----|------|-------|-------------|-------|----------------|

| AEN      | -       | х   | х    | _     | _           | x     | TTL            |

| BUSALE   | (6)     | R   | _    |       | R           | R     | TTL            |

| DACK#*   | _       | R   | D    |       |             | R     | TTL            |

| DRQ# (1) | -       | D   | R    | -     | _           | D     | TTL            |

| IOCHCK*  | R       | D   | _    | -     | D           | D     | oc             |

| IOCHRDY  | -       | D   | -    | R     | D           | D     | oc             |

| IOCS16*  | Х       | х   | х    | х     | х           | Х     | oc             |

| IORC*    | -       | -   | -    | -     | -           | -     | TRI            |

| IOWC*    | -       | -   | -    | -     | -           |       | TRI            |

| IRQ#(2)  | R       | D   | -    | -     | -           | D     | TTL            |

| LA#      | -       | -   | -    | -     | -           | -     | TRI            |

| SECMAST* | -       | D   | R    | -     | -           | -     | oc             |

| MCS16*   | Х       | Х   | х    | Х     | х           | Х     | oc             |

| MRDC*    | -       | R   | -    | D     | R           | -     | TRI            |

| MWTC*    | -       | -   | -    | -     |             | -     | TRI            |

| 840SC    | D       | R   | -    | -     | -           | -     | TTL            |

| MEMREF*  | -       | (7) | -    | R     | R           | -     | oc             |

| RSTDE(3) | D       | R   | R    | -     | -           | R     | TTL            |

| A#       | -       | -   | -    | -     | -           | -     | TRI            |

| <0700>   | -       | R   | -    | D     | R           | R     | TRI            |

| <1908>   | -       | -   | -    | -     | -           | -     | TRI            |

| SBHE#(4) | -       | -   | -    | -     | -           | -     | TRI            |

| D#       | -       | -   | -    | -     | -           | -     | TRI            |

| MEMR*    | (5)     | R   | -    | -     | R           | -     | TRI            |

| MEMW*    | -       | -   | -    | -     | -           | -     | TRI            |

| SYSCLK   | D       | R   | R    |       | R           | -     | TRI            |

| TC       | -       | -   | -    | -     | -           |       | TTL            |

| SRDY*    | -       | -   | -    | -     | -           | -     | ос             |

| Tab      | ole 5.4 | 1.2 | ADD- | -ON ( | CARD        | IS BU | JS OWNER       |

& HAS ENABLED MEMREF\*

NOTE: Primary CPU = PRI, Add-on card = ADD, DMA Controller = DMA, Refresh Controller = REF, Platform memory = MEM, Platform I/O = I/O, TTL = "ALS" or "LS", Open collector = OC, and Tristatable drivers/receivers = TRI.

"-" indicates that the respective signal line is not enabled or sensed by the resource.

"X" indicates a "don't care" condition. A resource can enable the signal but it will be ignored by other resources.

- (1) DRQ# can.be driven but will not be acted upon until the DMA Controller is bus owner.

- (2) Received by the Primary CPU via the Interrupt Controller and acted upon at the discretion of the Primary CPU when it is bus owner.

- (3) This signal must be sensed at all times and immediately acted upon if enabled.

- (4) Always received by the byte swapper hardware.

- (5) Driven by platform resources, the address is in the first 1MB of the address and either MRDC\* or MWTC\* signal lines.

- (6) Driven to the enabled level by platform hardware for the entire cycle.

- (7) Enabled by the add-on card that is bus owner.

#### 6.0 NON-BUS OWNER ATTRIBUTES

The Intel ISA bus has several unique attributes that are independent of bus ownership.

#### 6.1 MEMORY ADDRESS SPACE

The maximum memory address space supported by ISA bus is 16MB (24 address lines), but not all add-on card slots can support the full address space. When a bus owner accesses platform or add-on card slot memory, it must enable MRDC\* or MWTC\*; the platform hardware in turn enables the MEMR\* or MEMW\* lines if the access is in the first 1MB. Only the MEMR\*, MEMW\*, D<07..00>, and A<19..00> lines are attached to an [8] slot; thus [8] slot resources can only have an 8-bit data size and reside in the first 1MB of the memory address space. [8/16] add-on card slots receive all command, address, and data lines; thus these resources can respond as either 8- or 16-bit data resources anywhere in the memory address space. The access will be completed as a 16-bit cycle if MCS16\* is enabled.

Page 24

Page 25

#### NOTE

The ability of the platform or add-on card memory to respond as a 16-bit memory resource requires that MC816\* is enabled. MCS16\* is based on decoding LA<23..17>; thus the data size of each 128KB block on 128KB address boundaries must be entirely 8- or 16-bits. Different portions of each 128KB block cannot be of a different data size, as this would require decoding of the other address lines to generate MCS16\*.

#### CAUTION

The DRAM along with other bus resources require a refresh cycle. If the refresh operation is not executed every 15 usec., then a loss of data may occur.

#### ADD-ON CARD DESIGN FOCUS

The memory resource on the platform are of two types dynamic random access memory (DRAM) and EPROM space. The DRAM is either 16 or 32 data bits in size, depending the data size of the Primary CPU; but always appears as a 16-bit data resource to the add-on card. The EPROM contains the BIOS and is always 16-bits.

Refer to the Technical Reference Manual of an Intel ISA-based platform for information on memory mapping. A thorough study of memory usage is advised before attempting an add-on card design.

#### 6.2 I/O ADDRESS SPACE

, ·

The maximum I/O address space supported by the ISA bus is 64KB (16 address lines). All of the slots support 16 address lines. The first 256 bytes are reserved for the platform resource registers of Interrupt and DMA Controllers, timer/counter, RTC, and other elements for AT compatibility. The rest of the I/O address space accesses resources on the ISA bus. Refer to the Technical Reference Manual of an Intel ISA-based platform for information on I/O address space mapping.

#### ADD-ON CARD DESIGN FOCUS

Even though 16 address lines are available, traditionally only the first ten address lines have been decoded by the add-on cards for an I/O access. This causes the 1KB block referenced to each and every 1KB address boundary to be a repeat of the first 1KB block. Thus, the first 256 bytes that access XT/AT compatible platform resources is repeated at the beginning of each and every 1KB address boundary. Add-on card resources must not use this portion of the 1KB blocks.

If all of the add-on cards attached to the platform and the platform itself decode all 16 address lines, then the first 1KB block is not repeated throughout the address space. The XT/AT compatible resources only reside in the first 256 bytes cf the first 1KB.

#### 6.3 INTERRUPT STRUCTURE

The interrupt lines of the connectors are directly connected to the Intel 8259A Interrupt Controller. The Interrupt Controller will react to the interrupt on a transition of low to high. There are no interrupt acknowledge lines on the ISA bus. The resource must use a memory or I/O access by the bus owner for an acknowledgement of the interrupt.

#### ADD-ON CARD DESIGN FOCUS

The interrupt control lines are attached to all of the slots and are edge triggered. The add-on cards must allow the selection of the interrupt line at the time of installation to avoid conflict with already installed cards or platform resources.

#### 6.4 DATA SWAPPING

A PRIMARY CPU and an add-on card can execute either 8- or 16-bit access cycles. A cycle will be completed as 8-bits unless MCS16\* or IOCS16\* are enabled by the accessed resource. An 8-bit cycle is always completed as 8-bits independent of the size of the accessed resource. In either case, the platform must have the appropriate byte swapping hardware.

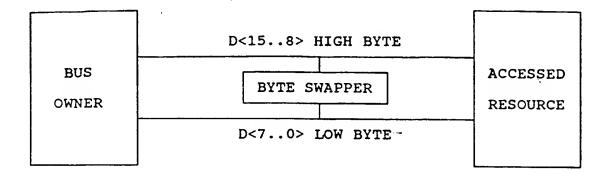

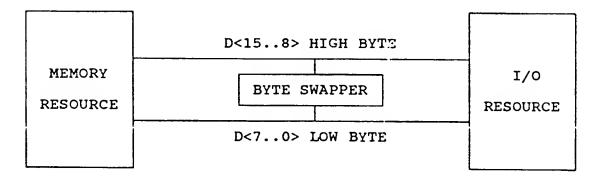

The byte swapper hardware resides on the platform. It adjusts for data size mismatch between resources. The mismatch can occur during access cycles as documented in Figure 6.4.1 and Table 6.4.1. The mismatch can also occur during DMA transfer cycles as documented in Figure 6.4.2 and Table 6.4.2.

Figure 6.4.1 BYTE SWAPPER HARDWARE FOR AN ACCESS CYCLE

#### Figure 6.4.2 BYTE SWAPPER HARDWARE FOR DMA TRANSFERS

Table 6.4.1 summarizes the bytes swapped for access cycles. The byte swapping hardware allows bus owners of 16-bit data size to access resources of 8-bit data size. The swapping activity between the HIGH BYTES and the LOW BYTES is summarized in Table 6.4.1. H>L denotes HIGH BYTE lines driven onto the LOW BYTE lines by the Byte Swapper hardware; H<L denotes the opposite. HH denotes the HIGH BYTE is sent between the bus owner and accessed resource without swapping. The LL denotes that the LOW BYTE is sent between the bus owner and accessed resource without swapping.

| BUS OWNER     |     |             |    | ESSED<br>DURCE | CYCLE COMPLETION |                                  |       |

|---------------|-----|-------------|----|----------------|------------------|----------------------------------|-------|

| DATA SBHE* AO |     | DATA XCS16* |    | DATA           | PATH             |                                  |       |

| SIZE(1)       |     | SIZE        |    | SIZE           | RD WR            |                                  |       |

| 8             | 1   | 0           | 8  | 1              | 8                | LL                               | LL    |

|               | 0   | 1           | 8  | 1              | 8                | H <l< td=""><td>H&gt;L</td></l<> | H>L   |

|               | 1   | 0           | 16 | 0              | 8                | LL                               | LL    |

|               | 0   | 1           | 16 | 0              | 8                | HH                               | HH    |

| 16            | 0 · | 0           | 8  | 1              | 8                | LL                               | LL    |

|               | 0   | 0           | 16 | 0              | 16               | HH/LL                            | HH/LL |

#### Table 6.4.1 BYTES SWAPPED FOR AN ACCESS CYCLE

NOTE:

(1) The bus owner is actually 16-bits in size but can do an 8-bit access.

Table 6.4.2 summarizes the bytes swapped for a DMA transfer cycle. The byte swapping hardware allows memory resources of 16-bit data size to interact with I/O resources of 8-bit data size. The swapping activity between the HIGH BYTES and the LOW BYTES is summarized in Table 6.4.2. H>L denotes HIGH BYTE lines driven onto the LOW BYTE lines by the Byte Swapper hardware; H<L denotes the opposite. HH denotes the HIGH BYTE is sent between the memory resource and the I/O resource without swapping. The LL denotes that the LOW BYTE is sent between the memory resource and the I/O resource without swapping.

| I/O<br>RESOURCE |          |   |             | MORY<br>OURCE | CYCLE COMPLETION |             |                   |

|-----------------|----------|---|-------------|---------------|------------------|-------------|-------------------|

| DATA            | SBHE* AO |   | DATA MCS16* |               | DATA             | PATH        |                   |

| SIZE            |          |   | SIZE        |               | SIZE             | RD WR       |                   |

| 8               | 1        | 0 | 8           | 1             | 8                | LL          | LL                |

| 8               | 1        | 0 | 16          | 0             | 8                | LL          | LL                |

| 8               | X        | 1 | 8           | 1             | 8                | LL          | LL                |

| 8               | X        | 1 | 16          | 0             | 8                | H>L         | H <l< td=""></l<> |

| 16              | 0        | 0 | 8           | 1             | 16               | ILLEGAL     |                   |

| 16              | 0        | 0 | 16          | 0             |                  | HH/LL HH/LL |                   |

#### Table 6.4.2 BYTES SWAPPED FOR A TRANSFER CYCLE

· ·

Page 29

#### 7.0 SIGNAL DESCRIPTIONS

This chapter lists and describes the seven signal groups that comprise the Intel ISA bus. The function of each signal is discussed in detail.

Each signal group has an [8] or [8/16] which denotes that this particular signal is available on an 8-bit only slot or an 8/16-bit slot, respectively.

#### 7.1 SIGNAL GROUPS

The Intel ISA bus contains seven groups of signals: ADDRESS, DATA, CYCLE CONTROL, CENTRAL CONTROL, INTERRUPT, DIRECT MEMORY ACCESS (DMA), and POWER. The input and output direction designations for each signal are referenced to the bus owner.

#### 7.1.1 ADDRESS SIGNAL GROUP

The address signal group consists of signals driven by the bus owner to specify data address.

#### **A<19..00>** [8][8/16]

Address signals are latched outputs driven by the bus owner. When the access is to the memory address space they represent the least significant 20 address bits and define a 1MB address space. When the access is to the I/O address space A<15...0> they contain the valid address and A<19...16> are undefined.

During refresh cycles A<07.... contain the valid address A<19...08> are undefined and should be tristated by all resources that can drive them.

#### ADD-ON CARD DESIGN FOCUS

The add-on card must be the bus owner to enable the MEMREF\* line. When the add-on card enables the MEMREF\* line, the address lines are driven by the Refresh Controller; they must be tri-stated by the add-on card.

#### LA<23..17> [8/16]

Unlatched address signals are driven by the bus owner. When the Primary CPU is bus owner, the LA lines are valid when BUSALE is asserted, but are not valid for the complete cycle. When the DMA Controller is bus owner, the LA lines must be valid prior to MRDC\* or MWTC\* and remain valid the entire cycle. When the access is to the memory address space they represent the seven most significant address bits. When the access is to the I/O address space or during refresh cycles these lines are driven to logical "O". During refresh cycles the unlatched address lines are undefined and should be tristated by all resources that can drive them.

# ADD-ON CARD DESIGN FOCUS

When the add-on card is bus owner these lines must be valid prior to MRDC\* or MWTC\* and remain valid the entire cycle. The add-on card must be the bus owner to enable the MEMREF\* line. When the add-on card enables the MEMREF\* line the address lines are driven by the Refresh Controller; they must be tri-stated by the

SBHE\* [8/16]. System Bus High Enable is enabled by the Primary CPU to indicate a transfer of data on lines D<15..8>. SBHE\* and A0 are used to determine which bytes are being transferred over the bus, as shown in Figure 6.4 and Table 6.4.

SBHE\* is not driven when the Refresh Controller is bus owner because no data swapping occurs; no actual data is read.

# ADD-ON CARD DESIGN FOCUS

When the add-on card is bus owner SBHE\* is used in the same fashion as it is used by the Primary CPU. The SBHE\* signal is tristated when the MEMREF\* line is enabled by the add-on card that is bus owner.

BUSALE [8][8/16] Bus Address Latch Enable is an address strobe driven by the Primary CPU to indicate when LA<23..17> are valid and can be latched. It also indicates when SBHE\* and A<19..00> are valid.

When the DMA Controller is bus owner the BUSALE is driven to a logical "1" by the platform because LA<23..17> and A<19..0> are valid prior to it enabling the command lines. When the Refresh Controller is bus owner the BUSALE line is driven to logical "1" by the platform because SA<19..00> are valid prior it enabling the MRDC\* and MEMR\* lines.

Page 31

# ADD-ON CARD DESIGN FOCUS

When the add-on card is the bus owner, the BUSALE is driven to logical "1" by the platform for the entire time that it is bus owner. Thus LA<23..17> and A<19..0> must be valid prior the addon card enabling the command lines.

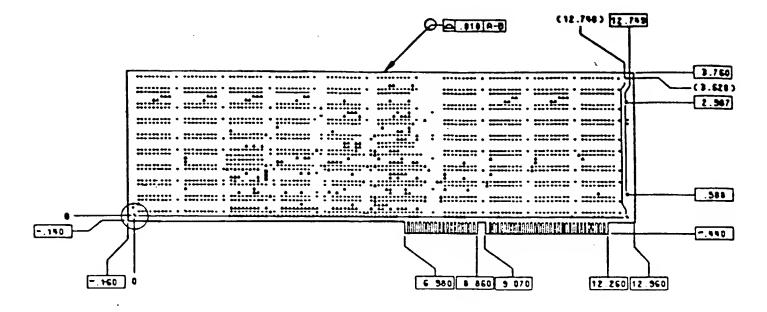

When the Primary CPU is bus owner and it is accessing an add-on card LA<23..19> is valid only for a short time; BUSALE is used by the add-on card to latch the address. When any resource other than the Primary CPU is bus owner, the BUSALE line remains enabled. A proposed input address circuit design for the add-on card to accommodate both situations is shown in Figure 7.1.1.

> LA23 D Q ISA - A23 LA22 D Q BUS - A22 ON BOARD ADDRESS LA19 D 0 A19 BUSALE -ENABLE 74XX373 (XX = LS or ALS)

# Figure 7.1.1 INPUT ADDRESS CIRCUIT

AEN [8][8/16]

Address Enable is enabled when the DMA Controller is the bus owner to indicate that a DMA transfer will occur. The enabling of the AEN line indicates to I/O resources to ignore the address lines which contain the memory address during DMA transfers. This line is disabled by the DMA controller when the Primary CPU or Refresh

# ADD-ON CARD DESIGN FOCUS

if an add-on card enables the SECMAST\* line, then the AEN is disabled by the DMA Controller to allow the add-on cards' access to the I/O address space. When the AEN line is enabled, the addon card should not be driving the bus unless it is part of the DMA

D<07..00> [8][8/16]

.

D<15..08> [8/16]

D15 is the most significant bit and D0 is the least significant bit. All 8-bit resources can connect only to the least significant eight data lines, D<07..00>. To support communication between 16bit bus owners and 8-bit resources, data swapping is supported by the BYTE SWAPPER circuitry on the baseboard.

Page 32

Figure 6.4 and Table 6.4 summarize the byte swapping function.

#### ADD-ON CARD DESIGN FOCUS

When the MEMREF\* line is enabled by the add-on card, the data lines must be tristated by the add-on card because no actual data is transferred during a refresh cycle.

#### 7.1.2 CYCLE CONTROL SIGNAL GROUP

This group of signals controls the duration and type of cycles. The group consists of six command signals, two ready signals, and three signals which specify the cycle size and type.

The command signals define the address space (memory or I/O) and the data direction (read or write). The ready signals modify the command pulse widths to lengthen or shorten the default cycle timings.

MRDC\* [8/16]

MEMR\* [8][8/16]

The Memory Read command (MRDC\*) is enabled by the bus owner to request a memory resource to drive the data bus with the contents of the memory location specified by LA<23..17>, A<19..00>. The System Memory Read command (MEMR\*) is identical in function to MRDC\*, except it is asserted only when the memory address is within the first 1MB. The MEMR\* signal is driven by the platform and is derived from the MRDC\* signal; thus it lags the MRDC\* signal by 10ns or less.

#### ADD-ON CARD DESIGN FOCUS

When the add-on card is bus owner it can only begin a bus cycle by enabling MRDC\*; MEMR\* is enabled by the platform if the access is in the first 1MB of the memory address space. When the add-on card enables the MEMREF\* line it must tri-state the

MRDC\* line because this line will be enabled by the Refresh Controller.

MWTC\* [8/16] MEMW\* [8][8/16] The Memory Write command (MWTC\*) is enabled when the bus owner is driving the data bus with data memory address location specified by LA<23..17> and A<19..00>. The System Memory Write (MEMW\*) is identical in function to MWTC\*, except it is asserted only when the memory address is within the first 1MB. The MEMW\* signal is driven by the platform and is derived from the MWTC\* signal; thus it lags the MWTC\* signal by 10ns or less.

Page 33

ADD-ON CARD DESIGN FOCUS When the add-on card is bus owner, it can only begin a bus cycle by enabling MRDC\*; MEMW\* is enabled by the platform if the access is in the first 1MB of the memory address space. When the add-on card enables the MEMREF\* line, it must tri-state IORC\* [8][8/16] I/O Read command (IORC\*) is enabled by the bus owner to request the accessed I/O resource to drive the data bus with the contents of the address specified by A15..00>. ADD-ON CARD DESIGN FOCUS When the add-on card enables the MEMREF\* line, it must tri-state IOWC\* [8][8/16] I/O Write command (IOWC\*) is enabled when the bus owner is driving the data bus for I/O address location specified by A<15..00>. ADD-ON CARD DESIGN FOCUS When the add-on card enables the MEMREF\* line, it must tri-state MCS16\* [8/16] Memory Cycle Select 16-bits is enabled by the accessed 16-bit memory resource to indicate to the bus owner that a 16-bit cycle may be executed. If this line is not enabled, then only an 8-bit cycle may be executed. The accessed resource generates MCS16\* based on a decode of LA<23..17>.

**NOTE** The DMA Controller and Refresh Controller will ignore MCS16\* during DMA transfers and refresh cycles, respectively.

# ADD-ON CARD DESIGN FOCUS

When the add-on card is in the access memory mode, it must enable the MCS16\* line if the memory on the card is 16-bit data size. When the add-on card is in the bus owner mode, A<15..00> may contain a value which may accidentally decode to a value that enables IOCS16\*; it must ignore this signal during memory

## IOCS16\* [8/16] I/O Cycle Select 16-bits is enabled by the accessed 16-bits I/O resource to indicate to the bus owner that a 16-bit cycle may be executed. If this line is not enabled, then only an 8-bit cycle may be executed. The accessed resource generates IOCS16\* based on a decode of A<15..00>.

NOTE

The DMA Controller and Refresh Controller will ignore IOCS16\* during DMA transfers and refresh cycles, respectively.

# ADD-ON CARD DESIGN FOCUS

When the add-on card is in the access memory and I/O mode it must enable this line if the memory on the card is 16-bit data size. When the add-on card is in the bus owner mode LA<23..17> it may accidentally decode to a value that enables MCS16\*; it must ignore this signal during I/O operations.

IOCHRDY [8][8/16]

I/O Channel Ready is an asynchronous signal driven by the accessed resource. It is disabled to force the bus owner to lengthen the bus cycle by inserting an integral number of wait states. When the bus owner is the PRIMARY CPU or add-on card, each wait state is an Intel ISA bus SYSCLK period, 125ns for an 8MHz clock rate. When the DMA Controller is bus owner, each wait state is two Intel ISA bus SYSCLK periods, or 250ns for an 8MHz clock rate. IOCHRDY is ignored during 0 wait state cycles.

NOTE

For DMA transfers I/O does not drive this line because the enabling of DRQ\* by the I/O resource can only be done when valid data can be received or sent. Only the memory resource involved with the DMA transfer can enable this signal.

Page 35

IOCHRDY must not be disabled for longer than 15 microseconds or refresh cycles will be "missed" and DRAM data failure may occur. ADD-ON CARD DESIGN FOCUS When the add-on card is in the bus owner it must receive IOCHRDY from the resource being accessed. When it is in the other modes it must drive this signal when it is ready to complete the cycle. CAUTION When some add-on cards are bus owners they ignore the IOCHRDY signal and run as default 8-bit or 16-bit normal type access memory cycle. Any add-on card that returns an IOCHRDY signal must determine if an accessing bus owner will be an add-on card that supports this function and thus allows the cycle to be lengthened. SRDY\* [8][8/16] 0 wait state is the only synchronous signal line on the Intel ISA bus. It is enabled by the accessed resource to request the Primary CPU or the add-on card to complete the current bus cycle without Even though this signal line is on the [8] slots, it is not used. It can only be used to access 16-bit memory resources installed in [8/16] slots when the Primary CPU or add-on card are bus owners. This signal is ignored during an I/O access or when the DMA Controller or Refresh Controller is the bus owner. ADD-ON CARD DESIGN FOCUS When the add-on card is in the bus owner it must receive SRDY\* from the resource being accessed in order to execute 0 wait state access cycle. When it is in the access memory mode it must drive this signal when it can support a 0 wait state access cycle. When some add-on cards are bus owners they ignore the SRDY\* signal and run as default 8-bit or 16-bit a Normal or Ready type access memory cycle.

MEMREF\* [8][8/16] MEMREF\* is enabled to indicate a DRAM refresh cycle. This signal is enabled by the Refresh Controller when it is bus owner.

#### ADD-ON CARD DESIGN FOCUS

When an add-on card is bus owner it can enable this signal line to request a refresh cycle. The cycle will be executed at that time by the Refresh Controller even though it is not bus owner.

## 7.1.3 CENTRAL CONTROL SIGNAL GROUP

· ·

The central control group consists of special timing, control, and error signals. The function of these signals is as follows.

**SECMAST\*** [8/16] This signal line can only be driven by the add-on card that has been granted bus ownership.

CAUTION

If SECMAST\* is enabled for longer than 15 microseconds, the add-on card must initiate refresh cycles by enabling the MEMREF\* line.

#### ADD-ON CARD DESIGN FOCUS

SECMAST\* is enabled by an add-on card to become bus owner after receiving the appropriate DACK#\* from the DMA Controller. After SECMAST\* is enabled, the add-on card must wait at least one SYSCLK period before driving the address and data group signals, and it must wait at least two SYSCLK periods before driving the cycle control group signals.

IOCHCK\* [8][8/16]

I/O Channel Check may be enabled by any resource to signal an error condition that cannot be corrected, such as a memory parity error. It must be enabled for at least 15ns. If the DMA or Refresh Controller are the bus owner, then this signal will be latched by platform hardware when enabled but not acted upon until the Primary CPU becomes bus owner.

#### ADD-ON CARD DESIGN FOCUS

If the add-on card is the bus owner when this signal is enabled, then the error will be latched by platform hardware when enabled but will not be acted upon until the Primary CPU becomes bus owner.

#### **RSTDEV** [8][8/16]

Reset Device is asserted by the Primary CPU to initialize all agents on the Intel ISA bus after power-up or during a low-voltage condition. The minimum enable time to ensure for reset is 1 millisecond.

#### ADD-ON CARD DESIGN FOCUS

The add-on card must immediately enter and remain in the reset condition when this signal is enabled. See Section 5.3 for more information about the reset condition.

SYSCLK [8][8/16]